Riscv

-

Page faults in emuriscv explained (and bugs fixed)

I’ve fixed two more bugs in the RISC-V emulator recently, both related to memory paging . The first one was caused by only supporting a one third of the possible page faults, the second one was …Breaking and fixing the RISC-V Store-Conditional instructions

Trying to debug the Linux boot process on the emuriscv RISC-V emulator has led me to discover another fun bug, one that appears when you don’t read the specification as thoroughly as you should. The …RISC-V Linux syscall table

Here’s a list of Linux system calls for the RISC-V architecture. Click the syscall name for the related manpage. See also syscalls(2) . RISC-V System call table Use the fuzzy filter box for search: …Fun with floating-point assembly (in RISC-V and x64)

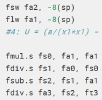

There was a fun little exercise in an old Fortran book that involved approximating a cube root using the Newton method to a specified accuracy. I’ve implemented this in multiple high-level languages …(Mis)understanding RISC-V ecalls and syscalls

After spending some time with emuriscv and attempting to boot Linux into a shell I realized that I’m doing something really wrong regarding system calls. RISC-V offers an ecall (Environment Call) …Online RISC-V disassembler

Making a nicer disassembler I’ve had a rudimentary disassembler in the emuriscv emulator, but compared to other disassemblers out there it was not very refined. Debugging and fixing the emulator …RISC-V supervisor mode

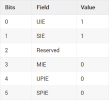

RISC-V features multiple privilege levels (machine, hypervisor, supervisor and user mode). The cores (harts) power up in machine mode, which is mandatory in all RISC-V implementations. Operating …Booting RISC-V on QEMU

For reference, I wanted to check how qemu boots RISC-V Linux. Loosely following a guide , I describe how to build and boot a Linux environment targeting the 32-bit RISC-V architecture. There are three …Revisiting RISC-V emulator in 2021

This week I’ve revisited my RISC-V emulator project emuriscv - https://github.com/jborza/emuriscv , as I’m still intrigued by the idea of booting Linux on my own CPU emulator. I’ve worked on and off …Writing a monitor console for emuriscv

As a follow up to the previous post Debugging things running in your emulator I thought it would be nice to write a monitor console for the emuriscv RISC-V emulator. With a monitor console one can …Updating the RISC-V Linux environment

As I planned to work some more on the emuriscv RISC-V emulator, I wanted to upgrade from Linux 4.15 and buildroot from 2018 to something more recent. Buildroot-2020-02 supports compiling the image …Test-driven emulator development

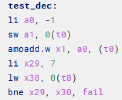

Test-driven development is a software development process where you write a test before writing a code that satisfies that test, then refactor and continuously validate that the requirements are still …Debugging things running in your emulator

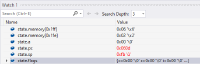

You’ve written an emulator, how do you debug anything running inside? In this post I’ll try to describe what I did (and thought of doing), starting from the most crude methods. Using the IDE and debug …Building up a RISC-V Linux with Buildroot

A friend told me about a cool new open-source instruction set architecture called RISC-V (pronounced risk-five). As I wanted to learn more about the architecture, I decided writing an RISC-V emulator …