Emuriscv

-

Page faults in emuriscv explained (and bugs fixed)

I’ve fixed two more bugs in the RISC-V emulator recently, both related to memory paging . The first one was caused by only supporting a one third of the possible page faults, the second one was …Breaking and fixing the RISC-V Store-Conditional instructions

Trying to debug the Linux boot process on the emuriscv RISC-V emulator has led me to discover another fun bug, one that appears when you don’t read the specification as thoroughly as you should. The …(Mis)understanding RISC-V ecalls and syscalls

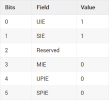

After spending some time with emuriscv and attempting to boot Linux into a shell I realized that I’m doing something really wrong regarding system calls. RISC-V offers an ecall (Environment Call) …RISC-V supervisor mode

RISC-V features multiple privilege levels (machine, hypervisor, supervisor and user mode). The cores (harts) power up in machine mode, which is mandatory in all RISC-V implementations. Operating …Booting RISC-V on QEMU

For reference, I wanted to check how qemu boots RISC-V Linux. Loosely following a guide , I describe how to build and boot a Linux environment targeting the 32-bit RISC-V architecture. There are three …Revisiting RISC-V emulator in 2021

This week I’ve revisited my RISC-V emulator project emuriscv - https://github.com/jborza/emuriscv , as I’m still intrigued by the idea of booting Linux on my own CPU emulator. I’ve worked on and off …Updating the RISC-V Linux environment

As I planned to work some more on the emuriscv RISC-V emulator, I wanted to upgrade from Linux 4.15 and buildroot from 2018 to something more recent. Buildroot-2020-02 supports compiling the image …Building up a RISC-V Linux with Buildroot

A friend told me about a cool new open-source instruction set architecture called RISC-V (pronounced risk-five). As I wanted to learn more about the architecture, I decided writing an RISC-V emulator …