Emulation

-

Breaking and fixing the RISC-V Store-Conditional instructions

Trying to debug the Linux boot process on the emuriscv RISC-V emulator has led me to discover another fun bug, one that appears when you don’t read the specification as thoroughly as you should. The …(Mis)understanding RISC-V ecalls and syscalls

After spending some time with emuriscv and attempting to boot Linux into a shell I realized that I’m doing something really wrong regarding system calls. RISC-V offers an ecall (Environment Call) …Online RISC-V disassembler

Making a nicer disassembler I’ve had a rudimentary disassembler in the emuriscv emulator, but compared to other disassemblers out there it was not very refined. Debugging and fixing the emulator …RISC-V supervisor mode

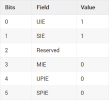

RISC-V features multiple privilege levels (machine, hypervisor, supervisor and user mode). The cores (harts) power up in machine mode, which is mandatory in all RISC-V implementations. Operating …Booting RISC-V on QEMU

For reference, I wanted to check how qemu boots RISC-V Linux. Loosely following a guide , I describe how to build and boot a Linux environment targeting the 32-bit RISC-V architecture. There are three …Revisiting RISC-V emulator in 2021

This week I’ve revisited my RISC-V emulator project emuriscv - https://github.com/jborza/emuriscv , as I’m still intrigued by the idea of booting Linux on my own CPU emulator. I’ve worked on and off …CHIP-8 on Nokia 3410

Mobile development like it’s 2002 I thought it’d be fun to develop something for a mobile phone. Thus I did a quick port of my previous CHIP-8 emulator from C to Java. Nokia 3410 looked like a fun …CHIP-8 emulators inconsistent behavior

CHIP-8 arithmetic behavior and VF variable I’ve been fiddling with CHIP-8 and writing a sample program in Octo - a CHIP-8 IDE/assembler with a nicer scripting language than raw opcodes. I wanted to …2 min read - chip8CHIP-8 emulator in C

CHIP-8 is one of the most popular target architectures for aspiring emulator writers. I’m planning to implement it in hardware, so I thought that writing a software emulator/interpreter would be …MCPU emulator (and ATTiny85 port)

MCPU is a neat minimal 8-bit CPU (CPU design by Tim Boescke in 2001, cpldcpu@opencores.org ) - see its opencores project file and GitHub repo . It fits into 32 macrocells on a CPLD and can operate on …Writing a monitor console for emuriscv

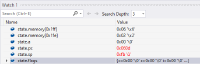

As a follow up to the previous post Debugging things running in your emulator I thought it would be nice to write a monitor console for the emuriscv RISC-V emulator. With a monitor console one can …Updating the RISC-V Linux environment

As I planned to work some more on the emuriscv RISC-V emulator, I wanted to upgrade from Linux 4.15 and buildroot from 2018 to something more recent. Buildroot-2020-02 supports compiling the image …Test-driven emulator development

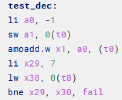

Test-driven development is a software development process where you write a test before writing a code that satisfies that test, then refactor and continuously validate that the requirements are still …Debugging things running in your emulator

You’ve written an emulator, how do you debug anything running inside? In this post I’ll try to describe what I did (and thought of doing), starting from the most crude methods. Using the IDE and debug …Building up a RISC-V Linux with Buildroot

A friend told me about a cool new open-source instruction set architecture called RISC-V (pronounced risk-five). As I wanted to learn more about the architecture, I decided writing an RISC-V emulator …Fantasy console on a console

Back in April 2019 I decided to get into emulation and thought about writing a simple one. I read about the MOS 6502 microprocessor and it looked promising as it was used in famous products such as …